Welcome.

Web page: schedule, book, exercises, slides, everything about the course. Also accessible from my personal web page.

E-mail: adavid@cs.aau.dk, also from my web page.

Updated from last year, changed content according to feedback and discussions with other lecturers.

No overlap with other courses.

Only place in the curriculum where you have a chance to learn about parallel programming.

Meaning of the course:

•Models for parallel machines and programs, programming paradigms, etc...

•Tools for parallelism: standard API s.a. MPI, pthreads, OpenMP (not in the course but you have materials in the book).

Claims to be modular and suitable for a wide variety of undergraduate and graduate level courses.

Covers traditional algorithms (sorting, graph, searching) and scientific computing algorithms (matrix, FFT).

Practical, code examples.

MPI, pthreads, also OpenMP (not in this course): 3 most widely used standards for writing portable parallel programs.

Recent (2003) and solid book.

Show the plan of the chapters (Figures/chap1.pdf).

Main goal (design, analysis, implementation) that needs important notions (sub-goals).

Short motivation:

•Hardware: Parallel computing has changed from tightly scalable message passing platforms to today's inexpensive clusters and multiprocessor machines.

•Software: Programming models have evolved from custom to standard APIs. MPI = standard message passing library, pthreads = thread library, OpenMP = directive based models.

Impact on process of **design**, **analysis**, and **implementation** of parallel algorithms: What this course is about.

There is another course dealing with the question of *concurrency*, in particular problems of deadlocks, livelocks, synchronization, condition variables, etc... I won't spend much time on the needed concepts, only what I need for this course (more pragmatic and practical approach).

•Specify: How to decompose a problem (most often sequential) into a set of parallel tasks to execute?

•Coordinate: Efficiency (control overhead in extra communication) and correctness issues (race conditions, deadlocks, livelocks).

Recall of race condition (several execution orderings may yield different results with the same program), deadlock (system not responding or doing anything), livelock (infinite loop without progress).

Algorithm standards: Actually in terms of API, now there are some.

Need to accelerate: Think of spending 2 years of development when the platform is going to be obsolete by the time you are finished.

Put a product name on all of these technologies to make it more concrete:

•Multi-core: X2 Athlon64, Intel's dual-core (P4 & new mobile CPU).

•Hyper-threading: Intel's technology to utilize the CPU better (switch thread instead of staying stalled on data).

•Multi-thread: Microsoft Xbox CPU, multithread triple core.

•Superscalar: Every modern GPU and CPU, several instructions in the same clock cycle (pipeline, different execution units).

Single processors have implicit lack of parallelism and have bottlenecks such as critical data paths and limited memory sub-system.

Example: multi-core recent design adopt simpler architectures replicated several times (no out-of-order execution), why? Complexity, efficiency/watt, die-size, price transistor/OPS (operation per second).

•Computational power: The demand for higher and higher computation power always grows, Moore's law is only the technological answer to that demand. We *want* to pursue Moore's law, that's why it still holds. The question is: How to continue from now on? (with the problems mentioned before).

•Memory/disk speed: Overall system performance is defined by CPU speed and the ability of the system to feed data to it. We have cheated so far by bridging the speed gap with caches that work thanks to the **data locality** property of almost all programs. Still we have both problems of **latency** and **bandwidth**. The same applies to disks (you are familiar with RAID technology).

•Parallel platforms: Linear increase in the number of processors of cache, bandwidth, etc... in total. The question is: How to use the increased resource such that the performance has a linear increase as well?

•Other arguments: Data communication (SETI@home a.k.a. search for extraterrestrial intelligence), constraints on location of data & resources that require distributed/parallel algorithms.

•Engineering & design: complex physical processes, geometric & mathematical modeling in context of parallel computers.

•Scientific applications: human genome sequencing, computational physics & chemistry.

•Commercial applications: multiprocessor & cluster machines for web & database servers.

•Embedded systems: cars, planes, etc... have many computer systems communicating via some network. 90% of computer systems are embedded systems.

•Gaming industry: Xbox 360 (triple core CPU + general multi vertex/pixel shader engine), PS3 with Cell processor (8 simple computational units + 1 G5 on one core).

I will follow the book, skipping sections from time to time but the order will be respected. References to sections are given on the web and reminded during the lectures (plan may change). Lectures are intended to teach you and help you read the book.

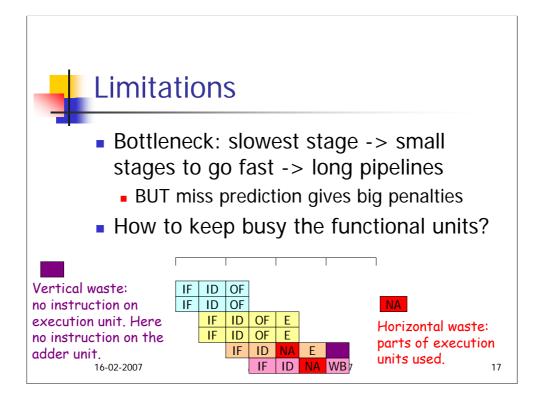

Bottlenecks of different kinds.

•Processor: less and less, though can be depending on some bad behaviors (branch miss prediction in large pipelines).

•Memory: more and more considering the speed gap between processor and memory, the problem being how to feed the processor with data so that it does not stay idle.

•Datapath: depends on programs and architecture, linked to previous ones.

Motivations for optimizing serial programs and why we talk about implicit parallelism: Sub-optimal serial code exhibits **unreliable** and **misleading** behaviors. Undesirable effects coming from poor cache utilization, bad branch prediction, etc ... that may become even worse in a parallel context (distribute data, synchronize, etc ...).

Similar characteristics in serial programs with intrinsic parallelism of modern processors (pipelines). Understanding architecture is the first step to good programming.

Already mentioned: Moore's law power x2 every 18 month, but for processor only. Global performance plagued by memory abysmal performance. Higher level of integration poses the question of how to best utilize transistors.

Functional units: MMU, FPU, etc usually part of the marketing buzz of microprocessor companies.

How to? That's the different architectures, not going into details but basically all processors are +/- RISC processors with a translation from assembler to microcode. Then most have branch prediction.

Overlapping stages: cut instructions in small pieces, one per cycle, and try to occupy all the stages. But why after all? Not better to have a super powerful one stage-do-all? Car factory: Imagine a fast factory where it takes 12h to complete one car. If there is one unit doing all, then it will be busy all the time and throughput would be 1 car per 12h. How to improve? Buy 11 other full scale units? Super expensive! Cut the bit unit in 12 smaller parts, 1h per part, every car needs 12h but throughput is 1 car per hour. 12x faster, cost efficient.

Branch prediction: try to keep the pipeline busy by filling it ahead, but if did it wrong, then need to flush it (and loose all the computations). P4: 20 stages, miss prediction means loose 20 cycles.

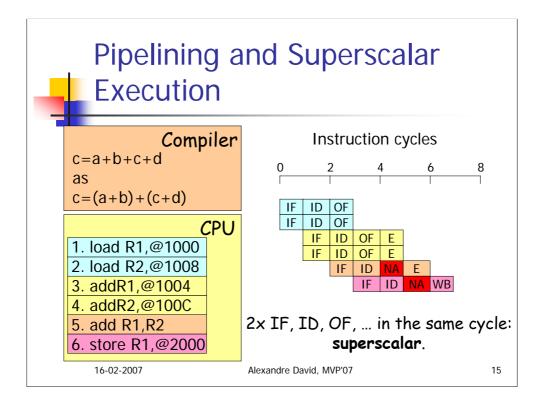

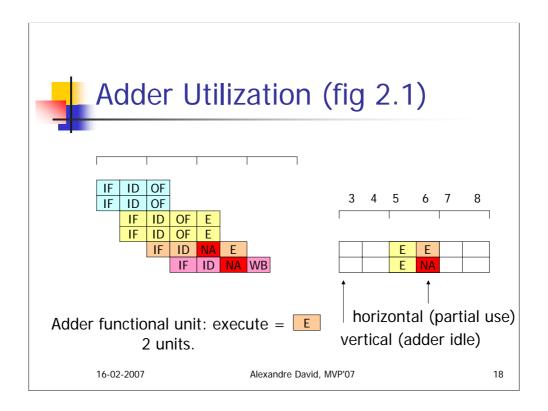

Dual issue or two-way superscalar execution.

IF: Instruction Fetch.

ID: Instruction Decode.

OF: Operand Fetch.

E: Instruction Execute.

WB: Write back.

NA: No Action.

Note: begin to execute 6<sup>th</sup> instruction at 4<sup>th</sup> clock cycle.

Compare the number of cycles without pipelining and/or superscalar.

Data dependency: needs previous results in order to continue computations. A=(B+C)\*D, we need B+C before computing \*D.

Resource dependency: needs functional units. A=B\*C+C\*D+D\*E+E\*F+F\*G, obviously not all \* can be done in parallel because of lack of functional units. Most processors are capable of out-of-order execution, not Xbox 360.

Intrinsic parallelism: Pipeline (multiple stages) & multiple functional units (superscalar) implement parallelism.

Modern processors: 4 way superscalar, 10-20 stage pipeline.

More explanation for fig 2.1.

Very Long Instruction Word Processors!

Superscalar schedulers are complex and expensive (transistors). VLIW design idea is to rely on the compiler to bundle instructions together, so that the scheduler becomes very simple.

The problem is most often how to feed the processor with continuous data so that it does not **stall**.

Latency is the time from the issue of a memory request to the time the data becomes available to the processor.

Bandwidth is the rate at which data can be pumped to the processor.

Example: water hose. Latency: time before first drop of water comes out. Bandwidth: rate flow of water.

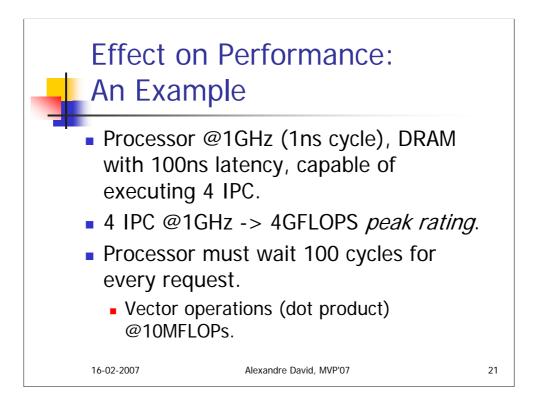

No cache in this example to simplify. It is still general enough since we can consider first access to some memory and take cache miss into account.

ALU: arithmetic and logical unit.

FPU: floating point unit.

Here absolute worst case scenario but still we loose a factor 100 in performance.

Common: Athlon 64 64K+64K L1, 1M L2. Pentium 4 more complicated NetBurst with execution trace cache (12K) and 16K L1, with 1M L2.

Now you have to think some time about why it helps. You know about cache hit ratio, cache miss, at least you've heard about it.

REMEMBER these two! They are common to almost all programs and are vital to cache performance.

For parallel computing, even more important: apart from the aggregate higher amount of cache that must be used wisely, we have more penalty for moving data around processors (or processor nodes).

That also explains the model numbering for AMD processors. ©

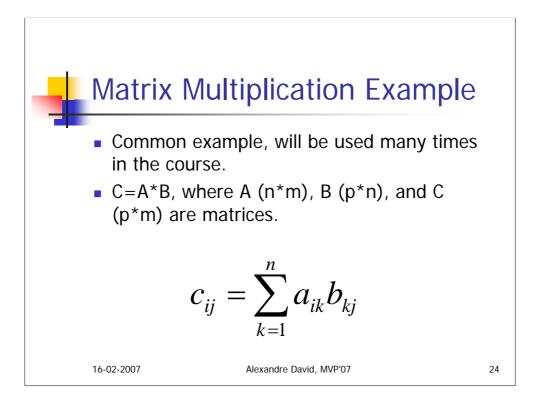

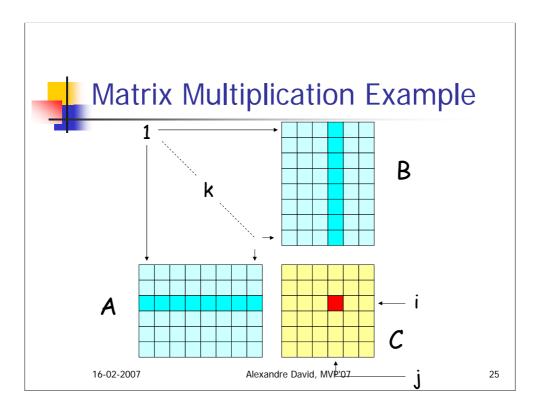

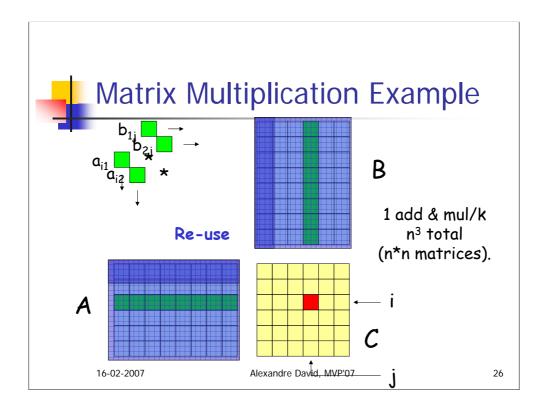

Compatible dimensions required. In practice n\*n.

Re-use: spatial and temporal localities. Intuitively:  $n^3$  accesses on  $2x n^2$  matrices (if  $n^*n$ ).

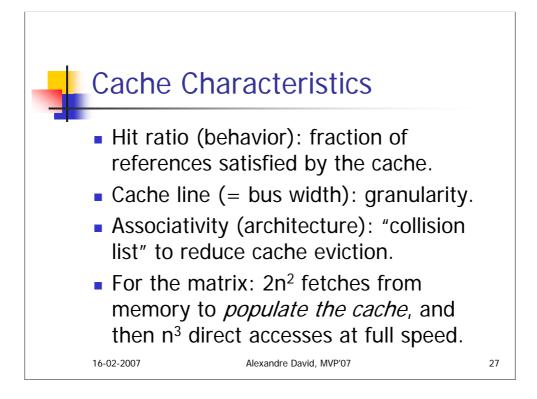

Data re-use is the keyword. Cache line: word granularity is too expensive and bad for spatial locality. 4 words usually for L2 (access to system bus), and internally 256-bit data bus for L1<->L2 (8 words).

The term *cache eviction* is not mentioned in the book and is missing. It is an important notion to know.

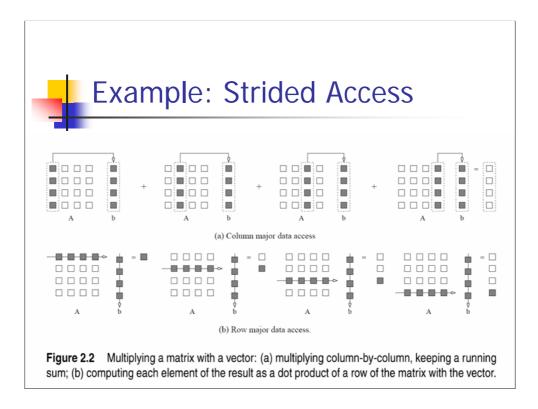

- a) Add vectors (temporary results) to get final result.

- b) Compute final result incrementally.

Strided access (a) yields poor performance.

Prefetching is like fetching the next cache line when possible (hardware decides), or same effect by reordering instructions (hardware or compiler) to issue loads long before usage. Works if consecutive words are accessed by consecutive instructions (spatial locality).

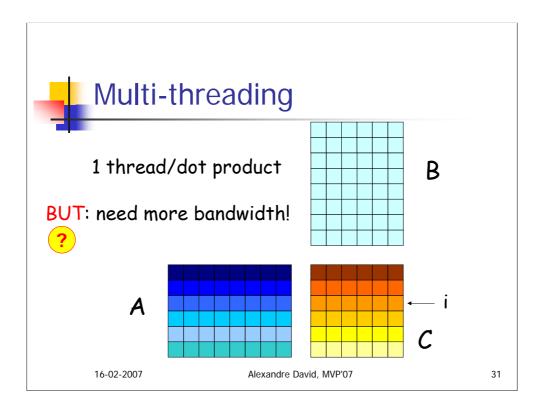

Multi-thread: switch to another thread when a thread stalls for data and keep the processor busy.

In fact, both solutions address the latency problem and exacerbate the bandwidth problem. That was probably the design idea behind RAMBUS, though no multi-threading at the time to use it! + the fact that latency was way higher than other systems.

Software: need to create the threads explicitly. Hardware: need support for multi-thread.

The 2 critical components both through logical and physical organizations.

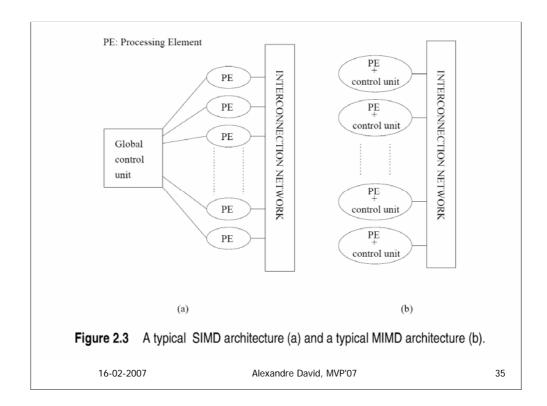

Processing units in parallel computers either operate under the centralized control of a single control unit or work independently.

•SIMD: A single control unit dispatches the same instruction to various processors or functional units.

•MIMD: Each processor has its own control unit and can execute different instructions on different data items.

PE: processing element.

Typically, SIMD implemented as special instruction sets on processors (MMX, SSE, SSE2, 3DNow!), and MIMD implemented as multiprocessor machines or clusters.

SIMD relies on the regular structure of computations (such as those in image processing).

A variant of MIMD, called single program multiple data streams (SPMD) executes the same program on different processors, which is often the case in practice.

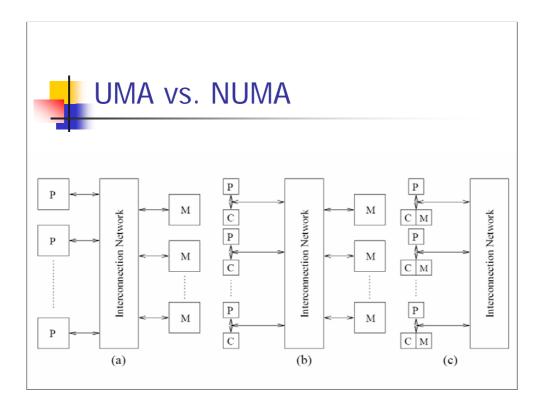

NUMA: non-uniform memory access. Cheaper and easier to implement. Need locality to perform well.

UMA: uniform memory access. Performant uniform access expensive.

Cheap and popular solution: cluster of MP machines connected via high bandwidth network.